# Design of Optimal Low Power Adaptive Filter for Reduction of Noise

<sup>1</sup>N. Hemalatha, <sup>2</sup>N. Nagarajakumari, <sup>3</sup>M. Sunitha and <sup>4</sup>D. Vasavi Pasanthi <sup>1</sup>P.G Student, Malineni Perumallu Educational Society's Group of Institutions, Guntur, Andhrapradesh <sup>2</sup>Assistant Professor, Malineni Perumallu Educational Society's Group of Institutions, Guntur, Andhrapradesh.

<sup>3</sup>Assistant Professor, R.V.R & J.C College of Engineering, Guntur, Andhra Pradesh. <sup>4</sup>Assistant Professor, GRIET, Hyderabad, Telegana.

Abstract: The present report presents an architectural approach to design an adaptive filter with low power consumption. Basically, an adaptive filter comprises of a variable filter and a filter coefficient updating algorithm. The variable filter is an FIR filter due to its stability, which has larger amplitude variations in input data and filter coefficients. As filtering part is the major contributor of power in an adaptive system, reducing switching activity and cancellation of multiplication will cause a significant reduction in power. To perform the adaptation process, that is convergence of output computed by the variable low power FIR filter to a desirable output least mean squares (LMS) and recursive least squares (RLS) algorithm is available. As one of the important applications of adaptive filtering, noise cancellation in communication system is performed on a signal with injected noise. The low power architecture for adaptive filter system which consists of a reconfigurable and low power FIR filter for filtering process and LMS algorithm for the adaptation process is designed .The low power adaptive filter architecture is verilog coded and simulated on Modelsim to check desired functionality .Then filter design is synthesized on Xilinx ISE suit for generating power report. Experimental results show significant reduction in power.

Keywords: Adaptive filter, FIR filter, least mean squares, recursive least squares.

# I. INTRODUCTION

As the scale of integration keeps growing, more and more sophisticated signal processing systems are being implemented on a VLSI chip [1]. These signal processing applications not only demand great computation capacity but also consume considerable amount of energy. Real-world signals which are analog in nature need to be processed so that the information contained in them can be displayed, analyzed or converted to other useful form, which is performed by a digital signal processing (DSP) system. Digital signal processing has been executing a major role in the current technical advancements such as noise cancellation, echo cancellation, voice prediction etc. So, for obtaining quick and acceptable solutions for these problems adaptive filtering techniques must be implemented other than standard DSP techniques. In general, filtering is one of the widely used operations in digital signal processing (DSP). A filter is a signal selection system that is used to extract desired signal from a noisy signal which consists of disturbances, whereas adaptive filter is particularly useful whenever the statistics of the input signals to the filter are unknown or time varying and the design requirements for fixed filters cannot easily be specified. The basic operation [2] of adaptive filter involves two processes: a filtering process and an adaptation process. The filtering process is usually fir filtering due to stability measures. The adaptation process uses an adaptation algorithm to update the filter coefficients according to the working environment. As filters are one of the major determinants of performance and power consumption of the whole system, there is an increased concern for designing low power filter structures. Digital filtering is an integral part of modern approaches to signal and image processing. This application is used in many domains (automation, telecommunications, biomedicine, etc.) As the paper aims to design a low power FIR adaptive filter, a summary of earlier efforts on reducing power consumption of FIR filter is discussed below. Several works on lowering power consumptions of FIR filters have been proposed earlier. Some previous works have tried to optimize the filter coefficient [3] while maintaining fixed filter [4] order. In those approaches, filter structures are simplified to add and shift operations and the power reduction is achieved by minimizing number of additions. However, one of the major drawbacks of such approaches is that the coefficient cannot be changed, once the filter order is fixed. There for those techniques are not applicable to the FIR filters with programmable coefficients. An improved algorithm is presented for the discrete optimization of FIR digital filter coefficients which are represented by a canonic signed-digit (CSD) code, i.e., numbers represent able as sums or differences of powers-of-two. The proposed search algorithm allocates an extra nonzero digit in the CSD code to the larger coefficients [5] to compensate for the very non uniform nature of the CSD coefficient distribution. This results in a small increase in the filter complexity [14]. For the design of low power FIR filters, approximate signal processing techniques [18] has also been used. In energy scalable system design [17], it is shown that sorting the data samples and coefficients before convolution operation has some energy quality characteristics. In this approach, for desirable energy quality behavior of FIR filter, MAC cycles that contribute significantly to the filter output is accumulated first by sorting. However, the overhead due to the real-time sorting of data samples is too large.

#### II. ARCHITECTURE OF LOW POWER ADAPTIVE FILTER

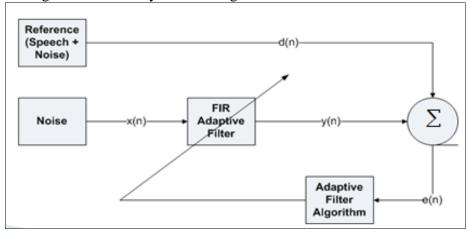

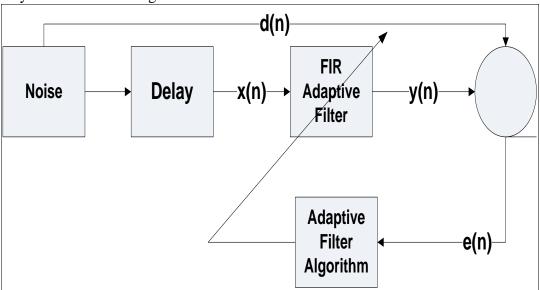

The adaptive filtering system contains four signals: reference signal, d(n), input signal, x(n), output signal, y(n), and the error signal, e(n). The filter, w(n), adaptively adjusts [6] its coefficients according to an optimization algorithm driven by the error signal.

Figure 1: Schematic diagram showing the architecture of low power adaptive filter system.

#### A. Typical Applications of Adaptive Filters

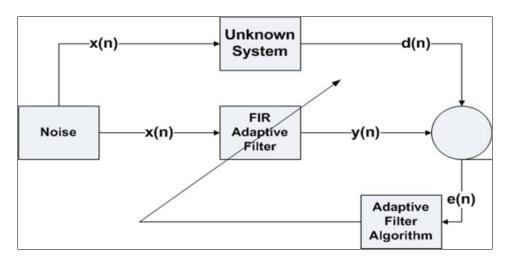

The adaptive filters are used in different applications, which are discussed below. Adaptive system identification (ASI): The system identification is an approach to model an unknown system. In this configuration the unknown system is in parallel with an adaptive filter, and both are excited with the same signal. When the output MSE is minimized the filter represents the [7] desired model. The structure used for adaptive system identification is illustrated in figure 2, where x(n) is an unknown system to be identified by an adaptive filter x(n). The signal x(n) excites y(n) and y(n), the desired

signal d(n) is the unknown system output, minimizing the difference of output signals y(n) and d(n), the characteristics of e(n) can be determined.

Figure 2: Schematic diagram showing the adaptive system identification.

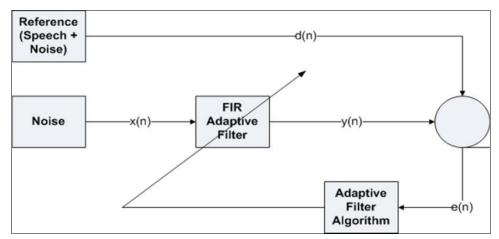

Adaptive Noise Cancellation (ANC): Noise control is an active or passive means of reducing sound emissions, often for personal comfort, environmental considerations or legal compliance. Active noise control is sound reduction using a power source. Passive noise control is sound reduction by noise-isolating materials such as insulation, sound-absorbing tiles, or a muffler rather than a power source. Active noise canceling is best suited for low frequencies. For higher [8] frequencies, the spacing requirements for free space and zone of silence techniques become prohibitive. In acoustic cavity and duct based systems, the number of nodes grows rapidly with increasing frequency, which quickly makes active noise control techniques unmanageable. Passive treatments become more effective at higher frequencies and often provide an adequate solution without the need for active control.

Figure 3: Schematic diagram showing the adaptive noise cancellation.

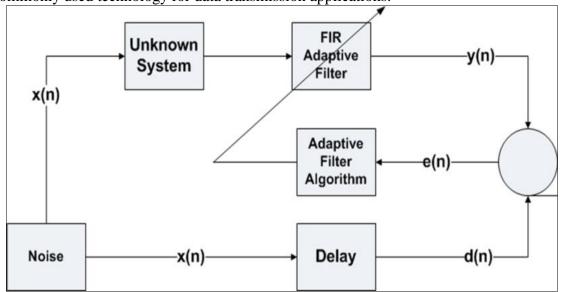

Adaptive Inverse (AI): The inverse modeling is an application that can be used in the area of channel equalization, for example it is applied in modems to reduce channel distortion resulting from the high speed of data transmission over telephone channels. In order to compensate the channel distortion we need to use an equalizer, which is the inverse of the channel's transfer function. High-speed data transmission through channels with severe distortion can be achieved in several ways, one way is to design the transmit and receive filters so that the combination of filters and channel results in an acceptable error from the combination of inter symbol [9] interference and noise; and the other way is

designing an equalizer in the receiver that counteracts the channel distortion. The second method is the most commonly used technology for data transmission applications.

Figure 4: Schematic diagram showing the adaptive inverse

Adaptive Prediction (AP): The linear prediction estimates the values of a signal at a future time. This model is wide usually in speech processing applications such as speech coding in cellular telephony, speech enhancement, and speech recognition. In this configuration the desired signal is a forward version of the adaptive filter input signal. When the adaptive algorithm convergences the filter represents a model for the input signal, this model can be used as a prediction model. The linear prediction system is shown in figure 5.

Figure 5: Schematic diagram showing the adaptive prediction

## B. Mathematical Analysis

P = E[x(n) d(n)] x(n) - Input signal

$x(n) = [x(n),x(n-1),....x(n-p)]^T$

w (n) – Weights of linear filter

$w(n) = [w(0), w(1), \dots, w(p)]^T = w^T$

y(n) – output of linear filter

$$y(n) = w^T x(n)$$

d(n) – desired signal

e(n) - error signal

$$e(n) = d(n) - y(n)$$

$$= d(n) - w^T x(n)$$

Mean Square Error (MSE) Function

Let, R be the square matrix.

$$R = E[x(n) x^{T}(n)]$$

$$MSE = \xi^2 = E[e^2(n)] = E[(d(n) - w^T x(n)) (d(n) - w^T x(n))]$$

$$MSE = \sigma^2_d - 2 w^T P + w^T R w$$

.....(1)

Where,

$$\sigma^2_d = E[d^2(n)]$$

The equation (1) is a quadratic function of component of weight w.

Gradient method is used to find out minimum performance surface. So, the gradient of mean square error performance [10] is denoted by

$$= \delta \xi^{2} = -2P + 2R w$$

$\delta w$

To obtain minimum MSE, the weight vector w is set at it optimal value Wopt where gradient is zero.

$$= 0 = -2 P + 2 R w$$

$$w = Wopt = R^{-1} P.....(2)$$

Equation (2) is called wiener- Hop equation.

Methods for searching performance surface:

- 1. Newton's method

- 2. Steepest descent method

Steepest descent method:

It is a method of gradient search that causes all components of the weight vector to be changed at each step and the changes are in the direction of the negative gradient of the performance surface.

From the definition:

W (n+1) = w (n) +

$$\mu$$

(-  $\nabla$  )

= w (n) -

$$\mu \delta \xi^2 / \delta w$$

$$= w(n) + 2 \mu [P - R w(n)]$$

Where ,  $\mu$  is a constant that regulates the step size.

Adaptive Filter Algorithm: There are two adaptation algorithm:

- 1. Least mean square (LMS) algorithm

- 2. Recursive least square (RLS) algorithm

#### C. Least mean square (LMS) algorithm

The LMS algorithm is an iterative formulation which solves, in the limit, the Wiener-Hopf equations recursively using a stochastic approximation to the method of steepest descent.

Wiener-Hopf solution for optimum filter weights shown in below equation

$$w = R-1 P = Wopt$$

Where,

$$R = E[x(n) x^{T}(n)]$$

$$P = E [x(n) d(n)]$$

To make exact measurements of the gradient vector at each iteration n, and if the step-size parameter is suitably chosen then the tap-weight vector computed by using the steepest descent algorithm would converge to the optimum wiener solution. The exact measurements of the gradient vector are not

possible and since that would require prior knowledge of both the autocorrelation matrix  $\mathbf{R}$  of the tap inputs and the cross [11] correlation vector  $\mathbf{P}$  between the tap inputs and the desired response, the optimum wiener solution could not be reached . Consequently, the gradient vector must be estimated from the available data when we operate in an unknown environment.

LMS algorithm is a noisy approximation of steepest descent algorithm. It is a gradient-type algorithm that updates the coefficient vector by taking a step in the direction of the negative gradient of the objective function.  $ww(nn+1)=ww(kk)-\mu 2 \delta Jw\delta w(n)$

where  $\mu$ , is the step size controlling the stability, convergence speed and misadjustment. To find an estimate of the gradient, the LMS algorithm uses an objective function considered as the instantaneous estimate of the mean square error, i.e.,  $J\mathbf{w} = ee2(nn)$  resulting in the gradient estimate  $\partial\partial JJ\mathbf{w}\mathbf{w}/\partial\partial ww(\mathbf{n}) = -2ee(nn) xx(nn)$ . In order to guarantee stability in the mean-squared sense, the step size  $\mu$  should be chosen in the range  $0 < \mu < 2/\text{tr}\{R\}$

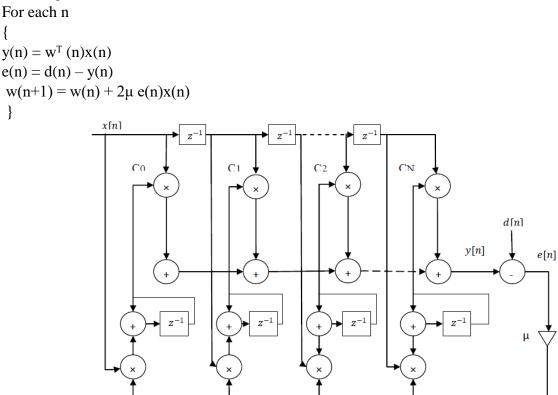

LMS Algorithm:

Figure 6: Schematic diagram showing the least mean square (LMS) algorithm

#### D. Recursive least square (RLS) algorithm

At each instant, RLS algorithm performs an exact minimization of the sum of the squares of the desired signal estimation errors. The computations begin with known initial conditions and based on the information's contained in the new [12] data samples, RLS algorithm updates the old estimates. These are its equations: To initialize the algorithm P(n) (inverse correlation matrix) should be made equal to  $\delta$ -1 where  $\delta$  (regularization factor) is a small positive constant.

## RLS Algorithm:

```

Y (n) =F (n) * U (n)

\propto (n) = G (n) - F (n) *U (n) \pi (n)=P(n-1) u(n)

K (n) = \lambda + \pi (n) u (n)

K (n) = P (n-1) u (n) k (n)

F (n) = F n-1) + K (n) \propto (n)

```

P1 (n-1) = K (n)\*

$$\pi$$

(n)

P (n) = { P (n-1) - P1(n-1)}/ $\lambda$

Where, F(n) = filter coefficients, K(n) = gain vector,  $\lambda$  = forgetting factor, P(n) = inverse correlation matrix of the input signal  $\alpha(n)$ ,  $\Pi(n)$  = positive constant.

#### E. Low Power Architecture

Space, power consumption and speed are major design issues in VLSI circuit. Power consumption in VLSI circuit (like in multipliers) is also data dependent. In this project primary goal is to reduce the dynamic power of the FIR filter. FIR filters are one of two primary types of digital filters used in Digital Signal Processing (DSP) applications. Multiplication is a very important operation in many digital signal processing (DSP) applications. The filters employed in mobile systems must be realized to consume less power and operate at high speed. The explosive growth in mobile computing and portable multimedia applications has increased the demand for low power digital signal processing (DSP) system. One of the most widely used operations performed in DSP is finite impulse response (FIR) filtering.

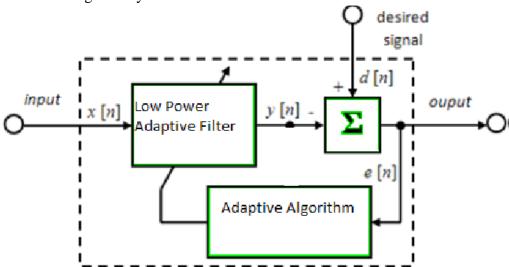

#### F. Low Power Adaptive Filter

It consists of a low power and reconfigurable FIR filter for filtering process and LMS algorithm for adaptation process. Finite impulse response (FIR) filters constitute the backbone of digital signal processing (DSP) systems. Power consumption is certainly the highest priority under consideration during the design-flow of state-of-the-art applications. Several techniques can be employed for improving the battery [13] autonomy of computationally demanding systems. Moreover, as modern electronic applications gradually become more complicated, throughput turns to be a crucial issue because several compromises must be made between hardware performance and power consumption by cancelling multiplication. More specifically, the dynamic power is reduced because it is directly proportional to switching activity.

Figure 7: Schematic diagram showing the low power adaptive filter

Power consumption of FIR filter is directly proportional to the amount of computation. To reduce the power consumption, the proposed FIR filter structure reduces switching activity and cancels multiplication. The architecture is reconfigurable because it changes the filter order dynamically by considering the amplitude of data samples and filter coefficients.

The architecture of reconfigurable FIR filter. It consists of three main sections. Amplitude Detector (AD), Multiplier Control Signal Decision window (MCSD) and a control signal generator. The

architecture reduces the power consumption by cancelling multiplication. More specifically, the dynamic power is reduced because it is directly proportional to switching activity.

#### III. IMPLEMENTATION OF FIR FILTER

The implementation of an FIR requires three basic building blocks

### A. Basic building blocks

Multiplier: In a DSP system the multiplier must be fast and must have sufficient precision (bit width) to support the desired application. A high quality filter will in general require more multiplications than one of lesser quality, so throughput suffers if the multiplier [14] is not fast. There are classes of filters that do not require multiplies.

Adder: Signal addition is a very basic DSP function. In an FIR filter additions are required in combination with multiplications, hence DSP microprocessors feature multiply- accumulate (MAC) units. Adders generally operate with just two inputs at a time.

Unit Delay: Unit delay provides a one sample signal delay. A sample value is stored in a memory slot for one sample clock cycle, and then made available as an input to the next processing stage. An *M*-unit delay requires *M* memory cells configured as a shift register.

## B. FIR Filter Structures

The analysis of linear, time-invariant FIR filter is generally carried out by using the Z transforms. A brief review of the Z-transform is presented. The filter structures characterizing the difference equations are represented using basic elements such as multipliers, time delays, and adders. The computational algorithm implementing Equation of an FIR filter can be conveniently represented in block diagram. It is done using the basic building blocks elements such as Multipliers, Adders, and Unit Delays.

Z Transform: The Z-transform is very useful role in the analysis and characterization of the linear time invariant systems. This is because the difference equations characterizing the discrete system are transformed into algebraic equations, which are much easier to manipulate.

Direct Form Structure: Direct structures for the Digital filter are those in which the real filter coefficients appear as multipliers. If X(z) is the filter input and Y(z) is the filter output then the transfer function H(z) is given as

Transpose Form Structure: The flow-graph-reversal theorem says that if one changes the directions of all the arrows, and inputs at the output and takes the output from the input [15] of a reversed flow graph, the new system has an identical input-output relationship to the original flow graph

#### C. Comparison of various Structures

The simplest of these structures, namely, the direct-form realizations. However, there are other more practical structures that offer some distinct advantages, especially when quantization effects are taken into consideration. The cascade, parallel and lattice structures exhibit robustness in finite word length implementations. The frequency-sampling has the [16] advantage of being computationally efficient when compared with alternative FIR realizations. Other filter structures are obtained by employing a state-space formulation for linear time-invariant system. Due to space limitations, state-space structures are not generally used.

## D. Significance of Higher Order Filter

However due to the stringent adjacent channel attenuation specifications of wireless communication standards, higher order filters are required for channelization and consequently the complexity and power consumption of the receiver will be high. As the ultimate aim of the future multi-standard wireless communication receiver is to realize its functionalities in mobile handsets, where its full

utilization is possible, low power and low area implementation of FIR channel filters is inevitable. For lower order filters, the approach [17] offers good trade-off between speed and area. But in general, the channel filters in wireless communication receivers need to be of high order to achieve sharp transition band and low adjacent channel attenuation requirements. For such applications, the approach in results is low speed of operation.

#### IV. SIMULATION AND SYNTHESIS RESULTS

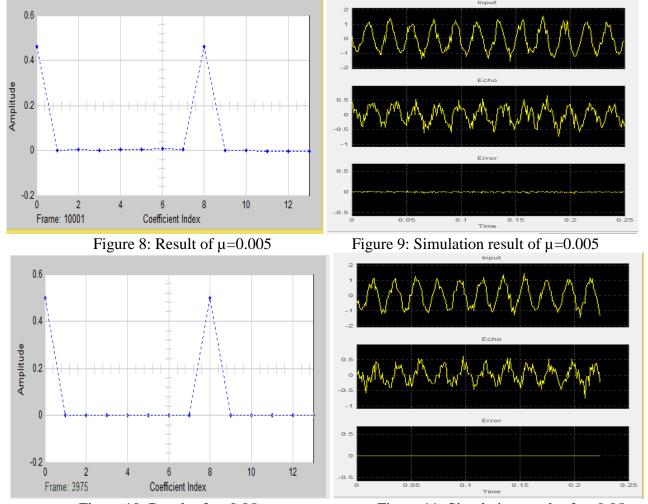

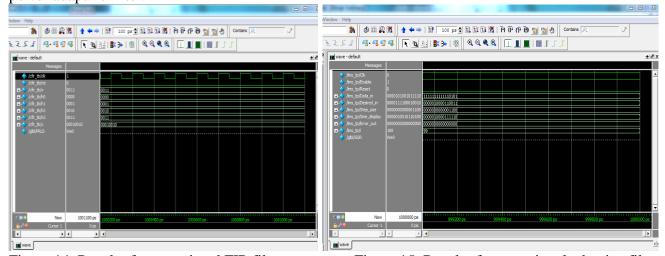

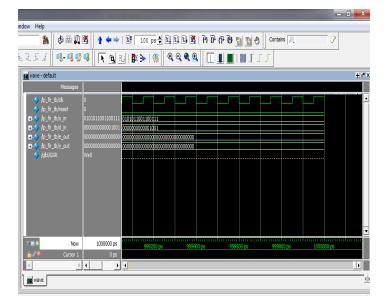

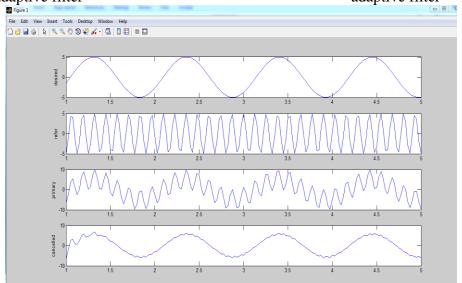

The low power adaptive filter is Verilog coded and simulated on ModelSim to check the desired functionality. The filter specifications are 16 bit data samples, 16 bit filter coefficients. For comparison we have verilog coded the conventional filter structures and low power conventional structure.

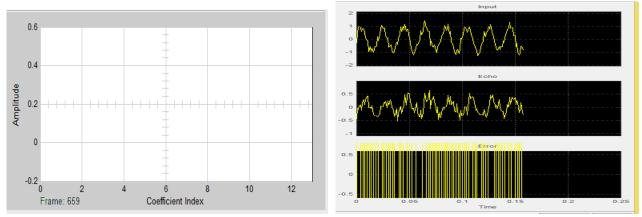

Figure 10: Result of  $\mu$ =0.05

Figure 11: Simulation result of  $\mu$ =0.05

Figure 12: Result of  $\mu$ =0.5

Figure 13: Simulation result of  $\mu$ =0.5

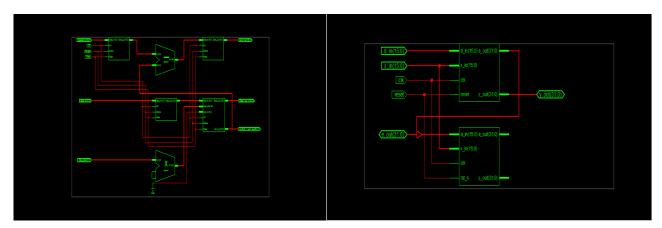

Figures 8, 9, 10, 11, 12 and 13 shows the ModelSim snapshots of conventional FIR filter. The simulation results of conventional and low power adaptive filter is shown in Figures. 14, 15 and 16. The filter structured in Verilog is synthesized on Xilinx ISE. The Xpower analysis on Xilinx provides the power report. Figures 17, 18 and 19 shows power report of conventional adaptive filter and low power adaptive filter.

Figure 14: Result of conventional FIR filter,

Figure 15: Result of conventional adaptive filter

Figure 16: Result of low power adaptive filter

#### V. CONCLUSION

In this work, low power architecture for adaptive filter is proposed. The low power adaptive filter consists of a reconfigurable low power FIR filter and the LMS algorithm. The LMS algorithm is used to update weights of reconfigurable filter with low complexity. The application of low power adaptive filter to noise cancellation is demonstrated using a signal with injected noise. The proposed low power adaptive filtering system can also be used for other applications such as system identification, echo cancellation etc.

Figure 17: RTL Schematic of conventional adaptive filter

Figure 18: RTL Schematic of Low Power adaptive filter

Figure 19: Result for implementation of adaptive filter

#### REFERENCES

- [1] Benard Widrow ,S.D. Stearns, Adaptive Signal Processing ,2nd Edition ,ISBN 978-81-317-0532-2 ,2009.

- [2] Li Tan, Jean Jiang, Digital Signal Processing Fundamentals and Application, 2nd Edition, ISBN 978-0-12-415893-1,2013.

- [3] Antoniou ,A.," Digital Filter",3rd Edition, Tata Mc. Graw Publications, 2001

- [4] Parhi K K., "A Systematic Approach For Design Of Digit-Serial Signal Processing Architectures", Circuits and Systems, 1991.

- [5] Saeid Mehrkanoon, Mahmoud Moghavvemi, Real time ocular and facial muscle artifacts removal from EEG Signals using LMS Adaptive Algorithm<sup>||</sup>, International Conference on Intelligence and Advanced System, 2007. IEEE

- [6] NJ Bershad, JCM Bermudez, An Affine Combination of Two LMS Adaptive Filter Transient Mean-Squre Analysis Signal Processing, IEEE Transactions, May 2008.

- [7] K. R. Borisagar, G. R. kulkarni Simulation and Comparative Analysis of LMS and RLS Algorithms Using Real Time Speech Input Signal GJRE, 2010.

- [8] Seok-Jae Lee, Ji-Woong Choi, Seon Wook Kim and Jongsun Park. (2011), —A Reconfigurable FIR Filter Architecture to Trade Off Filter Performance for Dynamic Power Consumption, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 12, pp.

- [9] R. Mahesh and A. P. Vinod .(2010), New reconfigurable architectures for implementing filters with low complexity, IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., vol. 29, no. 2, pp. 275–288.

- [10] R.Mahesh and A. P. Vinod.(2008), A new common subexpression elimination algorithm for realizing low complexity higher order digital filters, IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 227, no. 2, pp. 217–219.

- [11] Georgios Karakonstantis and Kaushik Roy (2007), An optimal algorithm for low power multiplier less FIR filter design using chebychev criterion I, IEEE ICASSP., pp. II-49 II-52

- [12] Vaseghy, S. V. Advanced Digital Signal Processing and Noise Reduction, Second Edition, Chichester Wiley, ISBN 0-470-84162-1, 2000.

- [13] H. Samueli, An improved search algorithm for the design of booth's multiplierless FIR filter with powers-of-two coefficients, IEEE Trans. CircuitsSyst., vol. 36, no. 7, pp. 1044–1047, Jul. 1989.

- [14] R. I. Hartley, Subexpression sharing in filters using canonical signed digitbooth's multipliers, IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 43, no. 10, pp. 677–688, Oct. 1996.

- [15] O. Gustafsson, A difference based adder graph heuristic for multiple constant multiplication problems, in Proc. IEEE Int. Symp. CircuitsSyst., 2007, pp. 1097–1100.

- [16] Sinha, A. Wang, and A. P. Chandrakasan.(2002), —Energy scalable system design, IEEE Trans. Very Large Scale Integr. Syst., vol. 10, no. 2, pp.135–145.

- [17] S. H. Nawab, A. V. Oppenheim, A. P. Chandrakasan, J. M. Winograd, and J. T. Ludwig (1997), Approximate signal processing, J. VLSI Signal Process., vol. 15, no. 1-2, pp. 177-200.